# PCIe X8 IP Core

IP Version: v2.2.0

**User Guide**

FPGA-IPUG-02243-1.3

March 2025

#### Disclaimers

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults, and all associated risk is the responsibility entirely of the Buyer. The information provided herein is for informational purposes only and may contain technical inaccuracies or omissions, and may be otherwise rendered inaccurate for many reasons, and Lattice assumes no obligation to update or otherwise correct or revise this information. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. LATTICE PRODUCTS AND SERVICES ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS, OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING ANY APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, BUYER MUST TAKE PRUDENT STEPS TO PROTECT AGAINST PRODUCT AND SERVICE FAILURES, INCLUDING APPROPRIATE REDUNDANCIES, FAIL-SAFE FEATURES, AND/OR SHUT-DOWN MECHANISMS. LATTICE EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information provided in this document or to any products at any time without notice.

#### **Inclusive Language**

This document was created consistent with Lattice Semiconductor's inclusive language policy. In some cases, the language in underlying tools and other items may not yet have been updated. Please refer to Lattice's inclusive language FAQ 6878 for a cross reference of terms. Note in some cases such as register names and state names it has been necessary to continue to utilize older terminology for compatibility.

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-IPUG-02243-1.3

# Contents

| Contents                                            |    |

|-----------------------------------------------------|----|

| Acronyms in This Document                           | 14 |

| 1. Introduction                                     | 15 |

| 1.1. Overview of the IP                             | 15 |

| 1.2. Quick Facts                                    | 15 |

| 1.3. IP Support Summary                             | 15 |

| 1.4. Features                                       | 16 |

| 1.4.1. Hard IP Limitations                          | 17 |

| 1.4.2. Soft IP                                      |    |

| 1.5. Licensing and Ordering Information             | 17 |

| 1.5.1. Ordering Part Number                         |    |

| 1.6. Hardware Support                               |    |

| 1.7. Speed Grade Supported                          |    |

| 1.8. Naming Conventions                             |    |

| 1.8.1. Nomenclature                                 |    |

| 1.8.2. Signal Names                                 |    |

| 2. Functional Description                           |    |

| 2.1. PCIe IP Architecture Overview                  |    |

| 2.2. Clocking                                       |    |

| 2.2.1. Clocking Overview                            |    |

| 2.3. Reset                                          |    |

| 2.3.1. Reset Overview                               |    |

| 2.3.2. Clock and Reset Sequence                     | 24 |

| 2.4. Protocol Layers                                |    |

| 2.4.1. ECC and Parity Data Path Protection          |    |

| 2.4.2. Error Handling                               | 26 |

| 2.4.3. LTSSM State                                  |    |

| 2.5. PHY Equalization (8 GT/s)                      |    |

| 2.5.1. Equalization Process                         |    |

| 2.5.2. Equalization Time Limit                      |    |

| 2.5.3. Equalization Methods                         |    |

| 2.5.4. Equalization Quality                         |    |

| 2.6. Multi-Function Support                         |    |

| 2.7. Power Management                               |    |

| 2.7.1. Power Management Supported by PCIe IP Core   |    |

| 2.7.2. Configuring Core to Support Power Management | 40 |

| 2.7.3. APSM LOs                                     | 40 |

| 2.7.4. APSM L1s                                     |    |

| 2.8. DMA Support                                    |    |

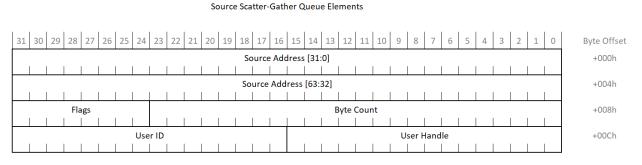

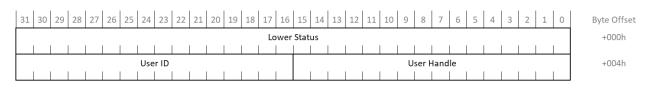

| 2.8.1. DMA Scatter-Gather and Status Queues         |    |

| 2.8.2. DMA Channel Programming and Operation        |    |

| 2.8.3. DMA Performance                              |    |

| 2.8.4. DMA Bypass Interface                         |    |

| 2.9. Non-DMA Support                                |    |

| 2.9.1. Non-DMA Overview                             |    |

| 2.9.2. Non-DMA Write                                |    |

| 2.9.3. Non-DMA Read                                 |    |

| 2.10. Interrupts                                    |    |

| 2.10.1. Generation of the Interrupts                |    |

| 2.10.2. Legacy Interrupt                            |    |

| 2.10.3. MSI Interrupt                               |    |

| 2.10.4. MSI-X Interrupt                             | 52 |

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

|    | 2.11. P          | Cle Endpoint Core Buffers                                                         | 53 |

|----|------------------|-----------------------------------------------------------------------------------|----|

|    | 2.11.1.          | PCI Express Credits                                                               | 54 |

|    | 2.11.2.          | Max Payload Size                                                                  | 54 |

|    | 2.12. H          | ard IP Interface                                                                  | 55 |

|    | 2.12.1.          | PHY Interface                                                                     | 55 |

|    | 2.12.2.          | TLP TX/RX Interface                                                               | 55 |

|    | 2.12.3.          | LMMI Interface                                                                    | 65 |

|    | 2.13. S          | oft IP Interface                                                                  | 66 |

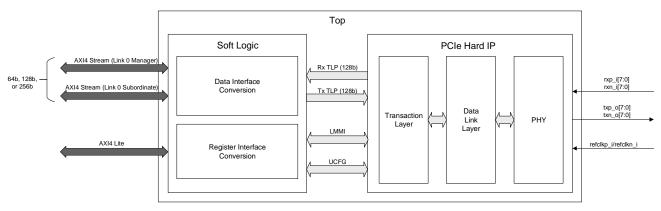

|    | 2.13.1.          | Data Interface Conversion                                                         | 66 |

|    | 2.13.2.          | Register Interface Conversion                                                     | 69 |

|    | 2.14. N          | 1ulti-Protocol Support                                                            | 69 |

| 3. | IP Para          | neter Description                                                                 | 70 |

|    | 3.1. G           | eneral                                                                            | 70 |

|    | 3.2. O           | ptional Port                                                                      | 71 |

|    | 3.3. Fl          | ow Control Update                                                                 | 72 |

|    | 3.4. F           | unction 0                                                                         | 73 |

|    | 3.4.1.           | Configuration                                                                     | 73 |

|    | 3.4.2.           | Base Address Register (BAR) [0 to 5]                                              | 74 |

|    | 3.4.3.           | Legacy Interrupt                                                                  | 75 |

|    | 3.4.4.           | MSI Capability                                                                    | 76 |

|    | 3.4.5.           | MSI-X Capability                                                                  | 76 |

|    | 3.4.6.           | Device Serial Number Capability                                                   | 77 |

|    | 3.4.7.           | PCI Express Capability                                                            |    |

|    | 3.4.8.           | Advance Error Reporting Capability                                                |    |

|    | 3.4.9.           | Atomic OP Capability                                                              |    |

|    | 3.4.10.          | Latency Tolerance Reporting Capability                                            |    |

|    | 3.4.11.          | Power Budgeting Capability                                                        |    |

|    |                  | Dynamic Power Allocation Capability                                               |    |

| 4. |                  | Description                                                                       |    |

|    |                  | lock and Reset Interface                                                          |    |

|    |                  | HY Interface                                                                      |    |

|    |                  | ransaction Layer Interface                                                        |    |

|    | 4.3.1.           | TLP Transmit Interface                                                            |    |

|    | 4.3.2.           | TLP Receive Interface                                                             |    |

|    |                  | attice Memory Mapped Interface (LMMI)                                             |    |

|    |                  | ower Management Interface                                                         |    |

|    |                  | XI-L Configuration Interface                                                      |    |

|    |                  | XI-4 Stream Data Interface                                                        |    |

|    | 4.7.1.           | AXI4-Stream Transmitter Interface Port Descriptions                               |    |

|    | 4.7.2.           | AXI4-Stream Receiver Interface Port Descriptions                                  |    |

|    |                  | MA Interface                                                                      |    |

|    |                  | nused Interface                                                                   |    |

| 5. |                  | r Description                                                                     |    |

| 5. |                  | ard IP Core Configuration and Status Registers                                    |    |

|    | 5.1.1.           | EP Configuration Settings                                                         |    |

|    | 5.1.2.           | mgmt_tlb (0x4_2000)                                                               |    |

|    | 5.1.2.           | mgmt_til (0x4_2000)                                                               |    |

|    | 5.1.3.<br>5.1.4. | mgmt_ftl (0x4_5000)                                                               |    |

|    | 5.1.4.<br>5.1.5. | mgmt_ftl_mf[7:1] (0x4_5000,0x4_6000,0x4_7000,0x4_8000,0x4_9000,0x4_A000,0x4_B000) |    |

|    |                  | CI Express Configuration Space Registers                                          |    |

|    | 5.2. P           | Type 00 Configuration Header                                                      |    |

|    | 5.2.1.           | Type 01 Configuration Header                                                      |    |

|    | 5.2.2.<br>5.2.3. | Capability and Extended Capability Address Locations                              |    |

|    | 5.2.3.<br>5.2.4. |                                                                                   |    |

|    | J.Z.4.           | Type 00 Configuration Registers                                                   |    |

| 5.2.5. PCI Express Capability                                                                    | 216 |

|--------------------------------------------------------------------------------------------------|-----|

| 5.2.6. Power Management Capability                                                               | 222 |

| 5.2.7. MSI-X Capability                                                                          | 223 |

| 5.2.8. MSI Capability                                                                            | 224 |

| 5.2.9. Advanced Error Reporting Extended Capability                                              | 225 |

| 5.2.10. ARI Extended Capability                                                                  | 227 |

| 5.2.11. Vendor-Specific Extended Capability                                                      | 228 |

| 5.2.12. Secondary PCI Express Extended Capability                                                | 229 |

| 5.2.13. ATS Extended Capability                                                                  | 230 |

| 5.2.14. DSN Extended Capability                                                                  |     |

| 5.2.15. Resizable BAR Capability                                                                 |     |

| 5.2.16. Power Budgeting Capability                                                               | 231 |

| 5.2.17. Dynamic Power Allocation Capability                                                      |     |

| 5.2.18. L1 PM Substates Extended Capability                                                      |     |

| 5.2.19. Latency Tolerance Reporting Capability                                                   |     |

| 5.3. DMA Configuration Space Registers                                                           |     |

| 6. Example Design                                                                                |     |

| 6.1. Example Design Supported Configuration                                                      |     |

| 6.2. Overview of the Example Design and Features                                                 |     |

| 6.3. Example Design Components                                                                   |     |

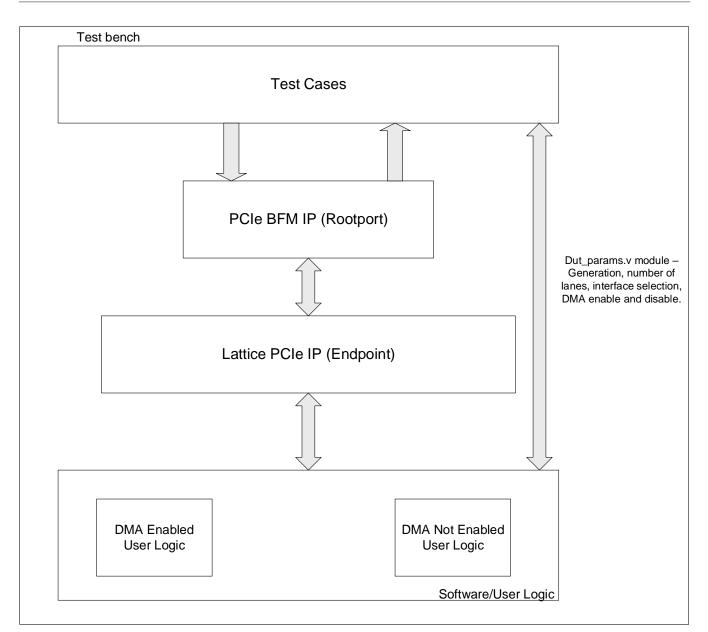

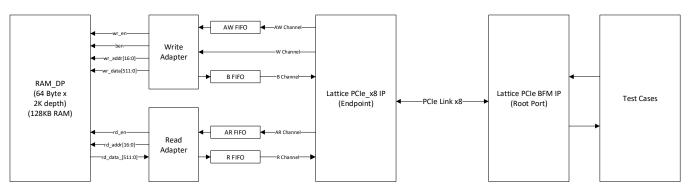

| 6.3.1. DMA Design                                                                                |     |

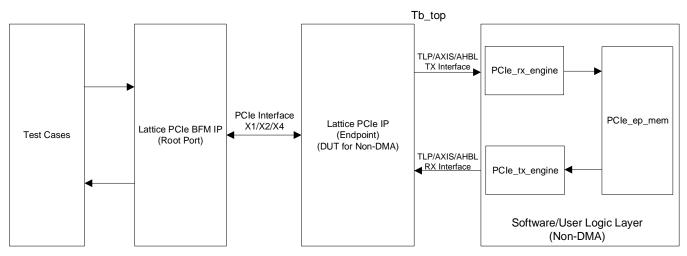

| 6.3.2. Non-DMA Design                                                                            |     |

| 6.4. Simulating the Example Design                                                               |     |

| 6.4.1. Running Functional Simulation (Non-DMA)                                                   |     |

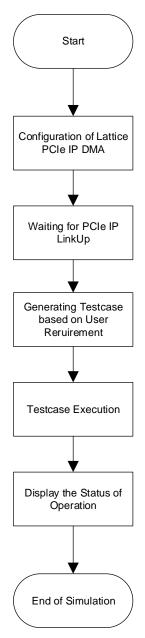

| 6.4.2. Running Functional Simulation (DMA)                                                       |     |

| 6.5. Generating the Example Design for Hardware                                                  |     |

| 6.5.1. DMA Variant                                                                               |     |

| 6.5.2. NON-DMA Variant                                                                           |     |

| 6.6. Design Test Case Examples                                                                   |     |

| 6.6.1. DMA Design                                                                                |     |

| 6.6.2. Non-DMA Design                                                                            |     |

| 6.7. Debugging Example Design Issues                                                             |     |

| 6.7.1. Signals to Debug                                                                          |     |

| 6.8. Limitations of the Example Design                                                           |     |

| 7. Designing with the IP                                                                         |     |

| 7.1. Generating and Instantiating the IP                                                         |     |

| <ul><li>7.1.1. Generated Files and File Structure</li><li>7.1.2. Design Implementation</li></ul> |     |

| 7.1.3. Timing Constraints                                                                        |     |

| 8. Debugging                                                                                     |     |

| 8.1. Debug Methods                                                                               |     |

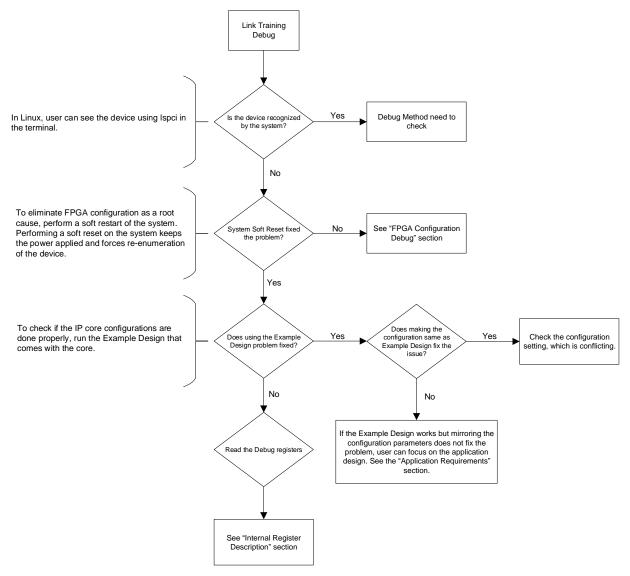

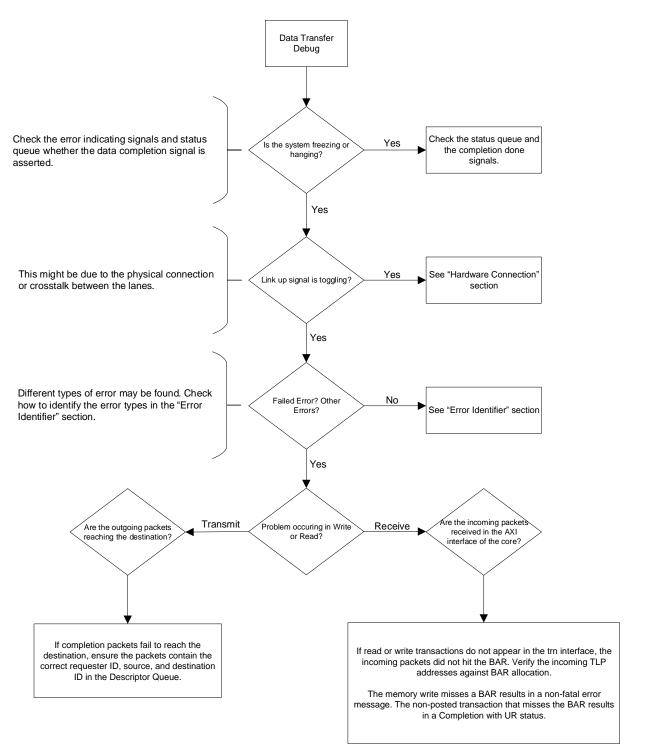

| 8.1.1. Debug Flow Charts                                                                         |     |

| 8.1.2. Internal Register Read for Debug                                                          |     |

| 8.1.3. PCIe Loopback Test                                                                        |     |

| 9. Design Consideration                                                                          |     |

| 9.1. DMA Based Design                                                                            |     |

| 9.2. Non-DMA Based Design                                                                        |     |

| Appendix A. Resource Utilization                                                                 |     |

| References                                                                                       |     |

| Technical Support Assistance                                                                     |     |

| Revision History                                                                                 |     |

|                                                                                                  |     |

# **Figures**

| Figure 2.1. Lattice PCIe x8 IP Core Block Diagram                  |    |

|--------------------------------------------------------------------|----|

| Figure 2.2. Lattice 8-lane SERDES/PCS + PCIe Hard-IP               |    |

| Figure 2.3. Lattice PCIe x8 Core Hard IP                           | 20 |

| Figure 2.4. PCIe IP Clock Domain Block Diagram for AXI-S Interface | 21 |

| Figure 2.5. PCIe IP Clock Domain Block Diagram for TLP Interface   |    |

| Figure 2.6. Reset Signals in Lattice PCIe IP Core                  | 23 |

| Figure 2-7. Clock and Reset Sequence Diagram                       |    |

| Figure 2.8. Source Scatter-Gather Queue Elements                   | 43 |

| Figure 2.9. Destination Scatter-Gather Queue Elements              |    |

| Figure 2.10. Status Queue Elements                                 |    |

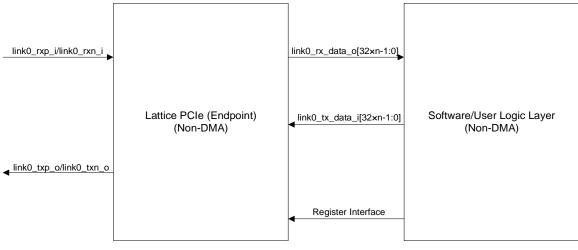

| Figure 2.11. Non-DMA Application Data Flow                         |    |

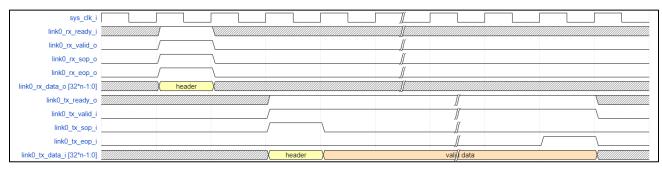

| Figure 2.12. Non-DMA Write Operation (TLP Data Interface)          |    |

| Figure 2.13. Non-DMA Read Operation (TLP Data Interface)           |    |

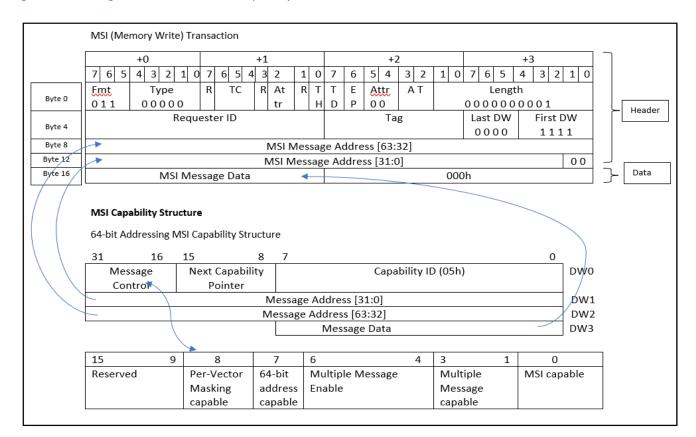

| Figure 2.14. MSI Capability Structure Variant                      |    |

| Figure 2.15. MSI Capability Structure Variant                      |    |

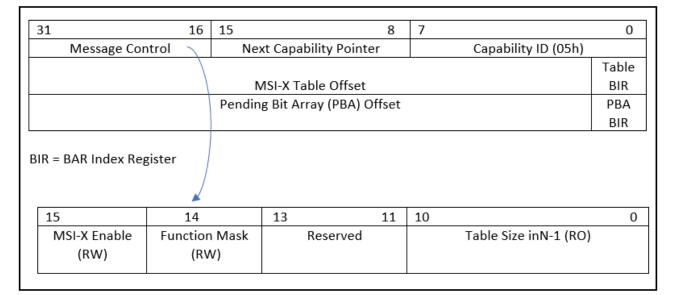

| Figure 2.16. MSI-X Capability Structure Variant                    |    |

| Figure 2.17. MSI-X Table Entries                                   |    |

| Figure 2.18. Pending Bit Array                                     |    |

| Figure 2.19. TLP Memory Request Header                             |    |

| Figure 2.20. TLP Memory Read Operation for Link0 (x4 Lane)         |    |

| Figure 2.21. TLP Memory Read Operation for Link0 (x2 Lane)         |    |

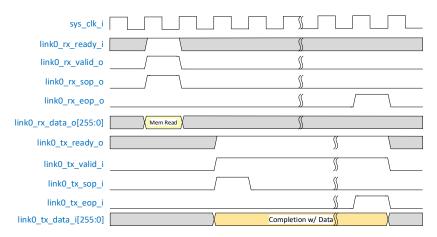

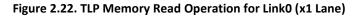

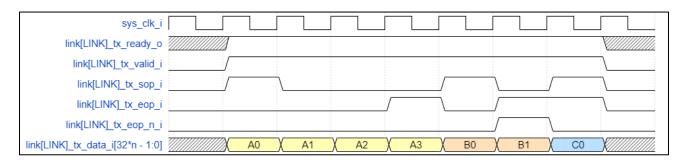

| Figure 2.22. TLP Memory Read Operation for Link0 (x1 Lane)         |    |

| Figure 2.23. Minimum link0_tx_ready_o Timing Diagram               |    |

| Figure 2.24. Wait State of link0_tx_ready_o Timing Diagram         |    |

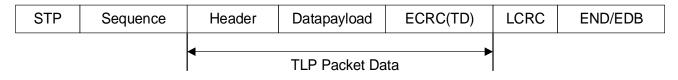

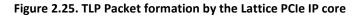

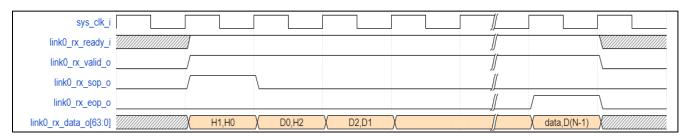

| Figure 2.25. TLP Packet formation by the Lattice PCIe IP core      |    |

| Figure 2.26. TLP Memory Write Operation for Link0 (x4 Lane)        |    |

| Figure 2.27. TLP Memory Write Operation for Link0 (x2 Lane)        |    |

| Figure 2.28. TLP Memory Write Operation for Link0 (x1 Lane)        |    |

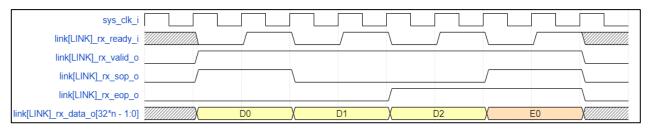

| Figure 2.29. Minimum link0_rx_ready_i Timing Diagram               |    |

| Figure 2.30. Wait State of link0_rx_ready_i Timing Diagram         |    |

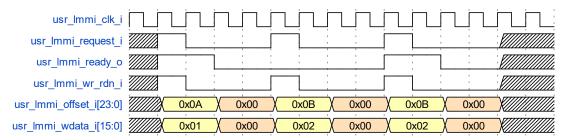

| Figure 2.31. LMMI Write Operation                                  |    |

| Figure 2.32. LMMI Read Operation                                   |    |

| Figure 2.33. AXI4-Stream Data Interface, AXI-L Register Interface  |    |

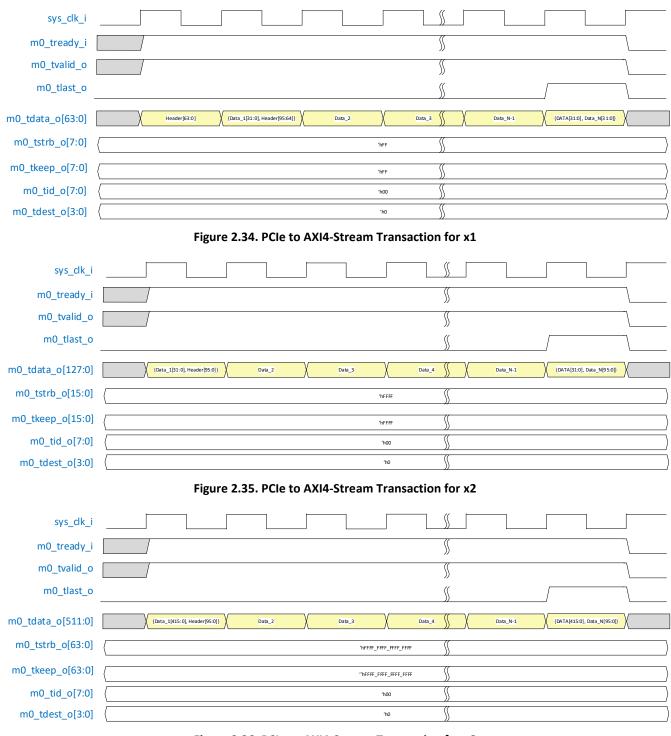

| Figure 2.34. PCIe to AXI4-Stream Transaction for x1                | 67 |

| Figure 2.35. PCIe to AXI4-Stream Transaction for x2                |    |

| Figure 2.36. PCIe to AXI4-Stream Transaction for x8                | 67 |

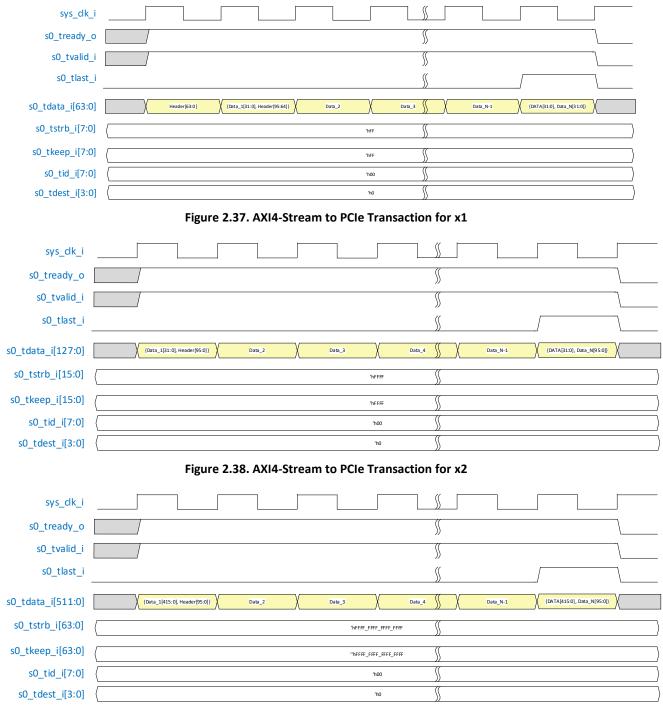

| Figure 2.37. AXI4-Stream to PCIe Transaction for x1                |    |

| Figure 2.38. AXI4-Stream to PCIe Transaction for x2                |    |

| Figure 2.39. AXI4-Stream to PCIe Transaction for x8                |    |

| Figure 2.40. PCIe Bifurcation                                      |    |

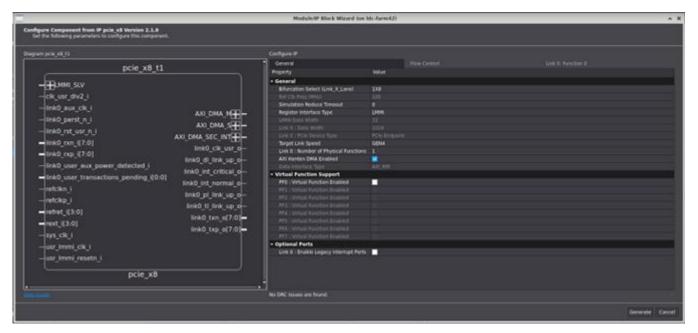

| Figure 3.1. Attributes in the General Tab                          |    |

| Figure 3.2. Attributes in the Optional Port Tab                    |    |

| Figure 3.3. Attributes in the Flow Control Update Tab              |    |

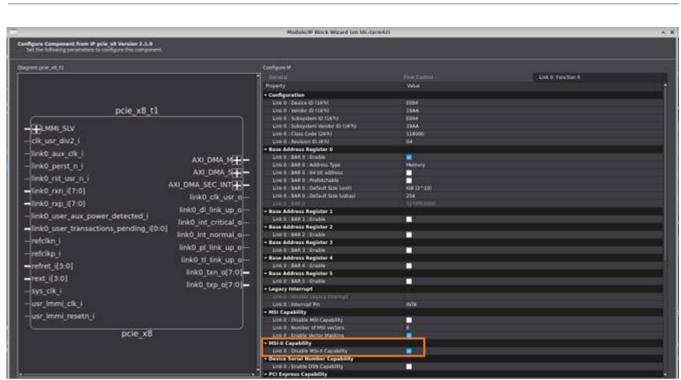

| Figure 3.4. Attributes in Function Configuration Tab               |    |

| Figure 3.5. Attributes in Participation Comparation rab            |    |

| Figure 3.6. Attributes in Eqacy Interrupt                          |    |

| Figure 3.7. Attributes in MSI Capability                           |    |

| Figure 3.8. Attributes in MSI-X Capability                         |    |

| Figure 3.9. Attributes in Device Serial Number Capability          |    |

| Figure 3.10. Attributes in PCIe Capability                         |    |

| Figure 3.11. Attributes in Advance Error Reporting Capability      |    |

|                                                                    |    |

| Figure 3.12. Attributes in Atomic OP Capability                    | /9 |

| Figure 3.13. Attributes in Latency Tolerance Reporting Capability                                           | 80  |

|-------------------------------------------------------------------------------------------------------------|-----|

| Figure 3.14. Attributes in Power Budgeting Capability                                                       |     |

| Figure 3.15. Attributes in Dynamic Allocation Capability                                                    |     |

| Figure 6.1. PCIe x8 IP Example Design Block Diagram                                                         |     |

| Figure 6.2. Components within the Harden DMA Design                                                         |     |

| Figure 6.3. Components within NON-DMA Design                                                                |     |

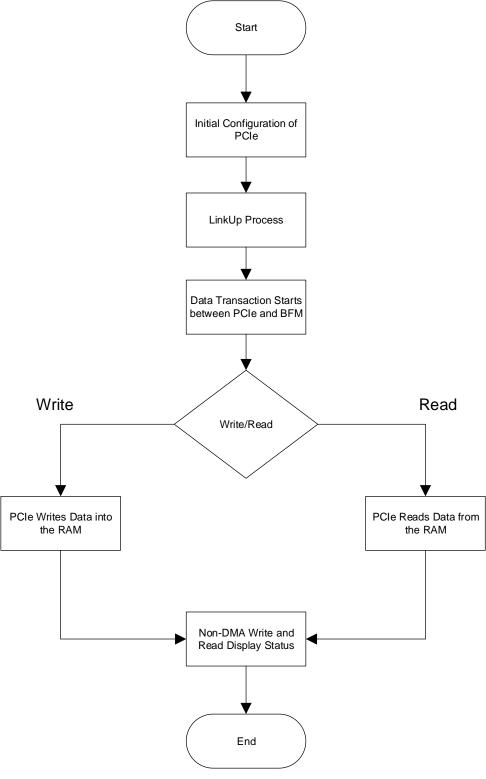

| Figure 6.4. Non-DMA Design Data Flow                                                                        |     |

| Figure 6.5. PCIe x8 IP Example Design Flowchart                                                             |     |

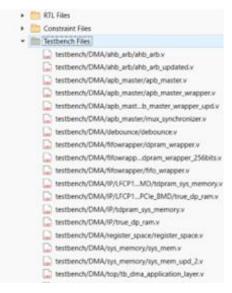

| Figure 6.6. Testbench Files                                                                                 |     |

| Figure 6.7. Project Naming                                                                                  |     |

| Figure 6.8. Simulation Top Module                                                                           |     |

| Figure 6.9. Simulation Setting                                                                              |     |

| Figure 6.10. Known Simulation Error                                                                         |     |

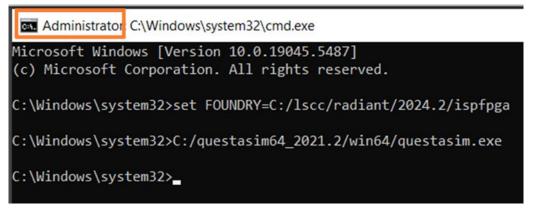

| Figure 6.11 System Environment Variable for Windows                                                         |     |

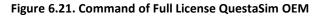

| Figure 6.12. Command of Full License QuestaSim OEM                                                          |     |

| Figure 6.13. Expected Log Printing                                                                          |     |

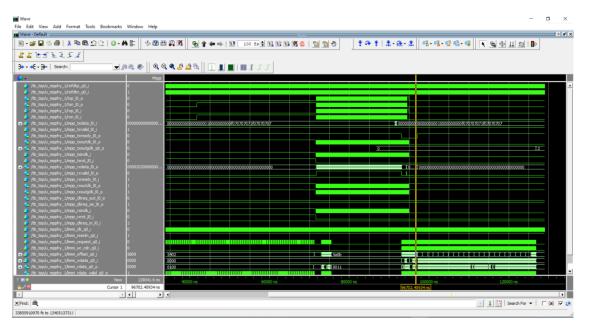

| Figure 6.14. Simulation Waveform                                                                            |     |

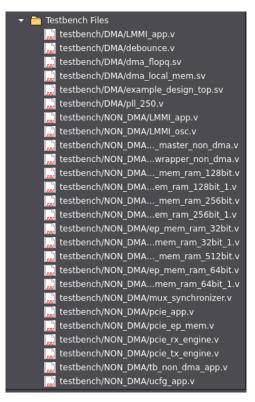

| Figure 6.15. Testbench Files                                                                                |     |

| Figure 6.16. Project Naming                                                                                 |     |

| Figure 6.17. Simulation Top Naming                                                                          |     |

| Figure 6.17. Simulation Top Naming                                                                          |     |

| Figure 6.19. Known Simulation Error                                                                         |     |

| Figure 6.20. System Environment Variable for Windows                                                        |     |

| Figure 6.21. Command of Full License QuestaSim OEM                                                          |     |

| Figure 6.22. Expected Log Printing                                                                          |     |

| Figure 6.22. Expected Log Printing                                                                          |     |

| Figure 6.23. IP Configuration for harden DMA Example Design – General Tab                                   |     |

| Figure 6.25. IP Configuration for Harden DMA Example design – Link 0: Function 0 Tab (Part 1)               |     |

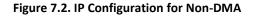

| Figure 6.25. IP Configuration for Non-DMA Example Design – General Tab                                      |     |

|                                                                                                             |     |

| Figure 6.27. WIDTH Parameter Adjustment in the example_design_top Module According to Bifurcation Selection |     |

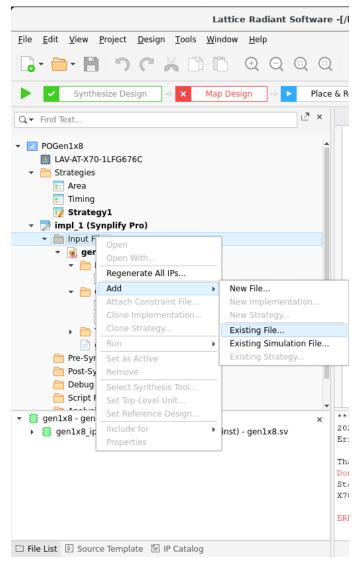

| Figure 7.1. Module/IP Block Wizard                                                                          |     |

| Figure 7.2. IP Configuration for Non-DMA (Conoral Tab)                                                      |     |

| Figure 7.3. IP Configuration for Harden DMA (General Tab)                                                   |     |

| Figure 7.4. IP Configuration for Harden DMA (Link 0: Function 0 Tab)<br>Figure 7.5. Check Generated Result  |     |

|                                                                                                             |     |

| Figure 7.6. Set IP Top Level Unit                                                                           |     |

| Figure 7.7. Select to Add Constraint File                                                                   | 266 |

| Figure 7.8. Select constraint.pdc from the Eval Folder                                                      |     |

| Figure 7.9. Project Compile Done                                                                            |     |

| Figure 7.10. Bitstream Not Generated due to the Virtual I/O Setting                                         |     |

| Figure 7.11. Timing Constraint File (.sdc) for the PCIe x8 IP                                               |     |

| Figure 7.12. PLL IP Configuration for Input Clock of 125 MHz                                                |     |

| Figure 7.13. Timing Constraints for PCIe x8 IP Example                                                      |     |

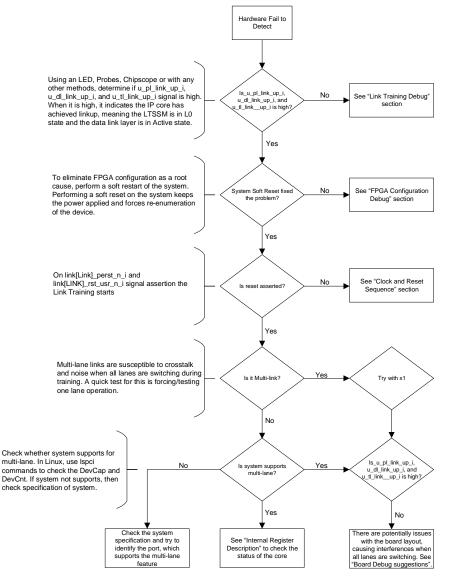

| Figure 8.1. Hardware Detection Failure Debugging Flow                                                       |     |

| Figure 8.2. Link Training Issue Debugging Flow                                                              |     |

| Figure 8.3. Checkbox to enable LTSSM Polling                                                                |     |

| Figure 8.4. Data Transfer Issue Debugging Flow                                                              |     |

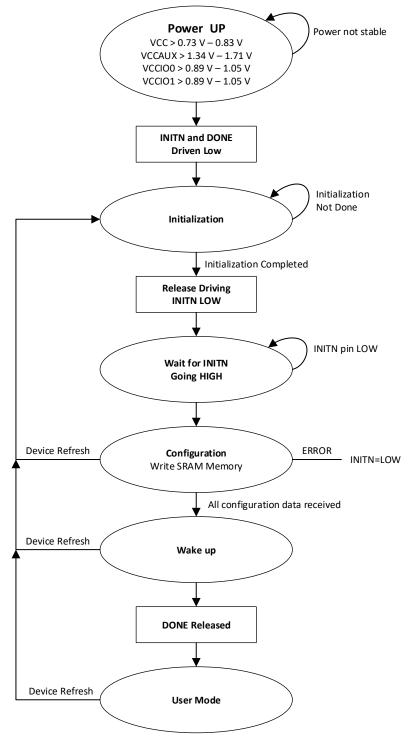

| Figure 8.5. Debugging the FPGA Configuration Issues Flow                                                    | 276 |

## Tables

| Table 1.1. Summary of the PCIe x8 IP                                                                    |    |

|---------------------------------------------------------------------------------------------------------|----|

| Table 1.2. Ordering Part Number                                                                         | 18 |

| Table 1.3. Lattice PCIe IP Core Supported Speed Grade                                                   | 18 |

| Table 2.1. General PCI Express Error List                                                               | 26 |

| Table 2.2. Physical Layer Error List                                                                    | 26 |

| Table 2.3. Data Link Layer Error List                                                                   | 27 |

| Table 2.4. Transaction Layer Error List                                                                 | 27 |

| Table 2.5. LTSSM State Definition                                                                       | 28 |

| Table 2.6. RX LOs State Description                                                                     | 31 |

| Table 2.7. Preset to Coefficient Conversion                                                             | 33 |

| Table 2.8. Simulation Data Throughput Using a Different Descriptor Size for FPGA-to-Host (F2H) Transfer | 47 |

| Table 2.9. Simulation Data Throughput Using a Different Descriptor Size for Host-to-FPGA (H2F) Transfer | 47 |

| Table 2.10. Register Access for Different Data Interfaces                                               | 48 |

| Table 2.11. Base Address to Enable Interrupt                                                            | 49 |

| Table 2.12. Legacy Interrupt Register                                                                   | 50 |

| Table 2.13. TLP Header Field                                                                            | 56 |

| Table 2.14. Data Byte Order                                                                             | 64 |

| Table 3.1. General Tab Attributes Description                                                           | 70 |

| Table 3.2. Optional Port Attributes                                                                     | 71 |

| Table 3.3. Flow Control Attributes                                                                      | 72 |

| Table 3.4. Function Configuration Tab Attributes                                                        | 73 |

| Table 3.5. BAR Tab Attributes                                                                           |    |

| Table 3.6. Legacy Interrupt Attribute Descriptions                                                      | 75 |

| Table 3.7. MSI Capability Attributes                                                                    |    |

| Table 3.8. MSI-X Capability Attributes                                                                  |    |

| Table 3.9. Device Serial Number Capability Attributes                                                   |    |

| Table 3.10. PCIe Capability Attributes                                                                  |    |

| Table 3.11. Advance Error Reporting Capability Attributes                                               |    |

| Table 3.12. Atomic OP capability Attributes                                                             |    |

| Table 3.13. Latency Tolerance Reporting Capability Attributes                                           |    |

| Table 3.14. Power Budgeting Capability Attributes                                                       |    |

| Table 3.15. Dynamic Allocation capability Attributes                                                    |    |

| Table 3.16. Function 1-3 Tab                                                                            |    |

| Table 4.1. Clock and Reset Ports                                                                        |    |

| Table 4.2. PHY Interface Descriptions                                                                   | 84 |

| Table 4.3. TLP Transmit Interface Ports                                                                 |    |

| Table 4.4. TLP Transmit Credit Interface Ports                                                          |    |

| Table 4.5. TLP Receive Interface Ports                                                                  |    |

| Table 4.6. TLP Receive Credit Interface Ports                                                           |    |

| Table 4.7. Lattice Memory Mapped Interface Ports                                                        |    |

| Table 4.8. AXI-L Configuration Interface Ports                                                          |    |

| Table 4.9. AXI-4 Stream Transmitter Interface Ports                                                     |    |

| Table 4.10. AXI-4 Stream Receiver Interface Ports                                                       |    |

| Table 4.11. DMA AXI4 Manager Write Interface                                                            |    |

| Table 4.12. DMA AXI4 Manager Read Interface                                                             |    |

| Table 4.13. DMA AXI4 Subordinate Write Interface                                                        |    |

| Table 4.14. DMA AXI4 Subordinate Read Interface                                                         |    |

| Table 4.15. DMA AXI4 Interrupt Interface                                                                |    |

| Table 4.16. Unused Interface                                                                            |    |

| Table 5.1. Register Access Abbreviations                                                                |    |

| Table 5.2. Hard PCIe Core Register Mapping                                                              |    |

| Table 5.3. CSR Values Recommended for EP Applications                                                   |    |

| ••                                                                                                      |    |

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

| Table 5.4. ltssm_simulation Register 0x0                             | 105 |

|----------------------------------------------------------------------|-----|

| Table 5.5. ltssm_cfg_lw_start Register 0x34                          | 105 |

| Table 5.6. ltssm_latch_rx Register 0x38                              | 106 |

| Table 5.7. ltssm_cfg Register 0x3c                                   | 106 |

| Table 5.8. ltssm_port_type Register 0x40                             |     |

| Table 5.9. ltssm_ds_link Register 0x44                               | 108 |

| Table 5.10. ltssm_detect_quiet Register 0x48                         | 109 |

| Table 5.11. ltssm_rx_det Register 0x4c                               | 109 |

| Table 5.12. ltssm_nfts Register 0x50                                 |     |

| Table 5.13. ltssm_ds_initial_auto Register 0x54                      | 110 |

| Table 5.14. ltssm_select_deemphasis Register 0x58                    | 110 |

| Table 5.15. ltssm_beacon Register 0x5c                               |     |

| Table 5.16. ltssm_mod_cpl Register 0x60                              |     |

| Table 5.17. ltssm_rx_elec_idle Register 0x64                         |     |

| Table 5.18. ltssm_compliance_toggle Register 0x68                    |     |

| Table 5.19. ltssm_prevent_rx_ts_entry_to Register 0x6c               |     |

| Table 5.20. ltssm_link Register 0x80                                 |     |

| Table 5.21. ltssm_ltssm Register 0x84                                | 114 |

| Table 5.22. ltssm_rx_l0s Register 0x88                               | 116 |

| Table 5.23. IO_to_rec Register 0x8c                                  |     |

| Table 5.24. ltssm_rx_detect Register 0x90                            |     |

| Table 5.25. ltssm_configured Register 0x94                           | 119 |

| Table 5.26. ltssm_direct_to_detect Register 0x98                     |     |

| Table 5.27. ltssm_equalization Register 0x9c                         |     |

| Table 5.28. ltssm_crosslink Register 0xa0                            |     |

| Table 5.29. Physical Layer Tx Underflow Error Status Register – 0xa4 | 120 |

| Table 5.30. Physical Lane Rx Status Registers                        |     |

| Table 5.31. pl_rx0 Register 0xa8 – Lane Rx Status 0 Register         |     |

| Table 5.32. pl_rx1 Register Oxac – Lane Rx Status 1                  |     |

| Table 5.33. pl_rx2 Register 0xb0 – Lane Rx Status 2                  |     |

| Table 5.34. pl_rx3 Register 0xb4 – Lane Rx Status 3                  | 128 |

| Table 5.35. pl_rx4 Register 0xb8 – Lane Rx Status 4                  |     |

| Table 5.36. debugself_crosslink Register 0xc0                        |     |

| Table 5.37. debug_rx_det Register 0xc4                               |     |

| Table 5.38. debug_force_tx Register 0xc8                             |     |

| Table 5.39. debug_direct_scramble_off Register 0xcc                  |     |

| Table 5.40. debug_force_scramble_off_fast Register 0xd0              |     |

| Table 5.41. balign Register 0xd4                                     |     |

| Table 5.42. debug_pipe_rx Register 0xe0                              |     |

| Table 5.43. debug_direct_to_loopback Register 0x100                  |     |

| Table 5.44. debug_loopback_control Register 0x104                    | 136 |

| Table 5.45. debug_loopback_master_5g Register 0x108                  |     |

| Table 5.46. debug_loopback_slave_5g Register 0x10c                   |     |

| Table 5.47. debug_loopback_master_8g_deemph Register 0x110           |     |

| Table 5.48. debug_loopback_slave_8g_deemph Register 0x114            |     |

| Table 5.49. debug_direct_to_loopback_status Register 0x118           |     |

| Table 5.50. debug_loopback_err_reset Register 0x11c                  |     |

| Table 5.51. debug_loopback_err Register 0x120                        |     |

| Table 5.52. phy_control Register 0x140                               |     |

| Table 5.53. phy_control_8g Register 0x144                            |     |

| Table 5.54. phy_eq_tx_override Register 0x148 F                      |     |

| Table 5.55. phy_eq_tx_max Register 0x14c                             |     |

| Table 5.56. phy_eq_tx_force Register 0x150                           |     |

| Table 5.57. phy_preset_to_coef_conv_control Register 0x15c           | 142 |

| Table 5.58. phy_preset_conv_tab_pre Register 0x160           |     |

|--------------------------------------------------------------|-----|

| Table 5.59. phy_preset_conv_tab_post Register 0x170          |     |

| Table 5.60. eq_control Register 0x180                        |     |

| Table 5.61. eq_ts_control Register 0x184                     |     |

| Table 5.62. eq_reduced_swing Register 0x188                  |     |

| Table 5.63. eq_method Register 0x1bc                         |     |

| Table 5.64. eq_fmerit_control Register 0x1c0                 |     |

| Table 5.65. eq_preset_method_control Register 0x1c4          |     |

| Table 5.66. eq_alg_method_control Register 0x1c8             |     |

| Table 5.67. eq_table_method_control Register 0x1cc           |     |

| Table 5.68. eq_table_method_table Register 0x1d0             | 148 |

| Table 5.69. eq_updn_control Register 0x240                   |     |

| Table 5.70. eq_firmware_control Register 0x280               | 150 |

| Table 5.71. eq_pre_cursor Register 0x290                     |     |

| Table 5.72. eq_post_cursor Register 0x2a0                    |     |

| Table 5.73. eq_status Register 0x2c0                         |     |

| Table 5.74. eq_status_error Register 0x2c4                   |     |

| Table 5.75. eq_status_preset_coef Register 0x2c8             |     |

| Table 5.76. eq_status_feedback_fom Register 0x2d0            |     |

| Table 5.77. eq_status_feedback_dir Register 0x2e0            |     |

| Table 5.78. eq_status_remote_fs Register 0x2e8               |     |

| Table 5.79. eq_status_remote_lf Register 0x2f4               | 154 |

| Table 5.80. eq_status_remote_precursor Register 0x300        |     |

| Table 5.81. eq_status_remote_postcursor Register 0x30c       | 155 |

| Table 5.82. pl_rx Register 0x33c                             |     |

| Table 5.83. pl_16g Register 0x340                            |     |

| Table 5.84. pl_tx_skp Register 0x344                         |     |

| Table 5.85. pl_tx_debug Register 0x348                       |     |

| Table 5.86. pl_ctrl Register 0x34c                           |     |

| Table 5.87. pl_ts_matching Register 0x350                    |     |

| Table 5.88. dl_retry_timeout Register 0x380                  |     |

| Table 5.89. dl_ack_timeout_div Register 0x384                |     |

| Table 5.90. dl_tx_ctrl Register 0x38c                        |     |

| Table 5.91. dl_ctrl Register 0x390                           |     |

| Table 5.92. dl_stat Register 0x394                           |     |

| Table 5.93. dl_ack_to_nak Register 0x398                     |     |

| Table 5.94. dl_inject Register 0x39c                         |     |

| Table 5.95. dllp_inject Register 0x3a0                       |     |

| Table 5.96. eq_status_table_control Register 0x3d8           |     |

| Table 5.97. eq_status_table_info Register 0x3dc              |     |

| Table 5.98. eq_status_table Register 0x3e0                   |     |

| Table 5.99. eq_capture_sel Register 0x3f0                    |     |

| Table 5.100. eq_capture Register 0x3f4                       |     |

| Table 5.101. phy_eq_tx_force_per_lane Register 0x400         |     |

| Table 5.102. phy_eq_tx_force_per_lane_8g_pre Register 0x404  |     |

| Table 5.103. phy_eq_tx_force_per_lane_8g_post Register 0x410 |     |

| Table 5.104. Simulation Register 0x0                         |     |

| Table 5.105. pm_aspm_l0s Register 0x40                       |     |

| Table 5.106. pm_aspm_l1 Register 0x50                        |     |

| Table 5.107. pm_aspm_l1_min Register 0x54                    |     |

| Table 5.108. pm_l1 Register 0x60                             |     |

| Table 5.109. pm_l1_min Register 0x64                         |     |

| Table 5.110. pm_l1pmss Register 0x68                         |     |

| Table 5.111. pm_l2 Register 0x70                             |     |

|                                                              |     |

|                                                                                | 470 |

|--------------------------------------------------------------------------------|-----|

| Table 5.112. pm_pme_to_ack_ep Register 0x80                                    |     |

| Table 5.113. pm_pme_to_ack_ds Register 0x84                                    |     |

| Table 5.114. pm_pme Register 0x88                                              |     |

| Table 5.115. pm_status Register 0x90                                           |     |

| Table 5.116. vc_rx_c Register 0x108                                            |     |

| Table 5.117. vc_rx_adv Register 0x10c                                          |     |

| Table 5.118. vc_rx_control Register 0x110                                      |     |

| Table 5.119. vc_rx_status Register 0x114                                       |     |

| Table 5.120. vc_rx_credit_status_cfg Register 0x120                            |     |

| Table 5.121. vc_rx_credit_status_p Register 0x124                              |     |

| Table 5.122. vc_rx_credit_status_n Register 0x128                              |     |

| Table 5.123. vc_rx_credit_status_c Register 0x12c                              |     |

| Table 5.124. vc_rx_f_oc_update_timer Register 0x130                            |     |

| Table 5.125. vc_rx_p_flow_ctrl Register 0x134                                  |     |

| Table 5.126. vc_rx_n_flow_ctrl Register 0x138                                  |     |

| Table 5.127. vc_rx_alloc_size Register 0x140                                   |     |

| Table 5.128. vc_rx_alloc_p Register 0x144                                      |     |

| Table 5.129. vc_rx_alloc_n Register 0x148                                      |     |

| Table 5.130. vc_rx_alloc_c Register 0x14c                                      |     |

| Table 5.131. vc_rx_alloc_error Register 0x150                                  | 179 |

| Table 5.132. vc_tx_np_fifo Register 0x180                                      |     |

| Table 5.133. vc_tx_status Register 0x184                                       | 180 |

| Table 5.134. vc_tx_credit_status_p Register 0x190                              | 180 |

| Table 5.135. vc_tx_credit_status_n Register 0x194                              | 181 |

| Table 5.136. vc_tx_credit_status_c Register 0x198                              | 181 |

| Table 5.137. vc_tx_credit_cleanup Register 0x19c                               | 181 |

| Table 5.138. tlp tx Register 0x1c4                                             |     |

| Table 5.139. fc_credit_init Register 0x1c8                                     | 182 |

| Table 5.140. simulation Register 0x0                                           |     |

| Table 5.141. decode Register 0x10                                              |     |

| Table 5.142. decode t1 Register 0x14                                           |     |

| Table 5.143. tlp processing Register 0x18                                      |     |

| Table 5.144. Initial Register 0x20                                             |     |

| Table 5.145. cfg Register 0x30                                                 |     |

| Table 5.146. ds port Register 0x34                                             |     |

| Table 5.147. us port Register 0x38                                             |     |

| Table 5.148. id1 Register 0x40                                                 |     |

| Table 5.149. id2 Register 0x44                                                 |     |

| Table 5.150. id3 Register 0x48                                                 |     |

| Table 5.151. Cardbus Register 0x4c                                             |     |

| Table 5.152. Interrupt Register 0x50                                           |     |

| Table 5.153. barO Register 0x60                                                |     |

| Table 5.154. bar1 Register 0x64                                                |     |

| Table 5.155. bar2 Register 0x68                                                |     |

| Table 5.156. bar3 Register 0x6c                                                |     |

| Table 5.157. bar4 Register 0x70                                                |     |

| Table 5.157. bar4 Register 0x70                                                |     |

| Table 5.159. exp_rom Register 0x78                                             |     |

| Table 5.159. exp_10in Register 0x78<br>Table 5.160. pcie_cap Register 0x80     |     |

| Table 5.160. pcie_cap Register 0x80<br>Table 5.161. pcie_dev_cap Register 0x84 |     |

|                                                                                |     |

| Table 5.162. pcie_link_cap Register 0x88                                       |     |

| Table 5.163. pcie_link_stat Register 0x8c                                      |     |

| Table 5.164. pcie_slot_cap Register 0x90                                       |     |

| Table 5.165. pcie_dev_cap2 Register 0x98                                       | 190 |

| Table 5.166. | pcie_link_ctl2 Register 0xa0                 | .197 |

|--------------|----------------------------------------------|------|

| Table 5.167. | pm_cap Register 0xc0                         | .198 |

| Table 5.168. | pm Register 0xc4                             | .199 |

| Table 5.169. | pm aux Register 0xc8                         | .199 |

| Table 5.170. | ari cap Register 0xe0                        | .200 |

| Table 5.171. | aer_cap Register 0x100                       | .200 |

|              | msi_cap Register 0xe8                        |      |

|              | msix_cap Register 0xf0                       |      |

|              | msix_table Register 0xf4                     |      |

|              | msix_pba Register 0xf8                       |      |

|              | vsec_cap Register 0x110                      |      |

|              | sris_cap Register 0x120                      |      |

|              | dsn_cap Register 0x130                       |      |

|              | dsn serial Register 0x134                    |      |

|              | pwr_budget_cap Register 0x150                |      |

|              | dpa_cap Register 0x158                       |      |

|              | dpa_xlcy Register 0x15c                      |      |

|              | dpa_alloc Register 0x160                     |      |

|              | ltr_cap Register 0x180                       |      |

|              | l1pmss cap Register 0x188                    |      |

|              | atomic_op_cap Register 0x1cc                 |      |

|              | Base Address for mgmt_ftl_mf                 |      |

|              | Function Register 0x8                        |      |

|              | us_port Register 0x38                        |      |

|              | id1 Register 0x40                            |      |

|              | id2 Register 0x44                            |      |

|              | id3 Register 0x44                            |      |

|              | Cardbus Register 0x4c                        |      |

|              |                                              |      |

|              | Interrupt Register 0x50                      |      |

|              | bar0 Register 0x60                           |      |

|              | bar1 Register 0x64                           |      |

|              | bar2 Register 0x68                           |      |

|              | bar3 Register 0x6c                           |      |

|              | bar4 Register 0x70                           |      |

|              | bar5 Register 0x74                           |      |

|              | exp_rom Register 0x78                        |      |

|              | msi_cap Register 0xe8                        |      |

|              | msix_cap Register 0xf0                       |      |

|              | msix_table Register 0xf4                     |      |

|              | msix_pba Register 0xf8                       |      |

|              | dsn_cap Register 0x130                       |      |

|              | dsn_serial Register 0x134                    |      |

|              | Type 00 Configuration Header                 |      |

|              | Type 01 Configuration Header                 |      |

|              | Capability and Extended Capability Items     |      |

|              | Type 00 Configuration Registers              |      |

|              | PCI Express Capability                       |      |

|              | Power Management Capability                  |      |

|              | MSI-X Capability                             |      |

|              | MSI Capability                               |      |

|              | Advanced Error Reporting Extended Capability |      |

|              | ARI Extended Capability                      |      |

|              | Vendor-Specific Extended Capability          |      |

| Table 5.219. | Secondary PCI Express Extended Capability    | .229 |

| Table 5.220. ATS Extended Capability                                | 230 |

|---------------------------------------------------------------------|-----|

| Table 5.221. DSN Extended Capability                                |     |

| Table 5.222. Resizable BAR Capability                               |     |

| Table 5.223. Power Budgeting Capability                             | 231 |

| Table 5.224. Dynamic Power Allocation (DPA) Capability              | 232 |

| Table 5.225. L1 PM Substates Extended Capability                    | 232 |

| Table 5.226. Latency Tolerance Reporting (LTR) Capability           | 233 |

| Table 5.227. DMA Configuration Space Registers                      | 234 |

| Table 6.1. PCIe x8 IP Configuration Supported by the Example Design | 240 |

| Table 6.2. Non-DMA Design Status Ports Description                  | 259 |

| Table 6.3. Non-DMA Signals to Debug Description                     | 259 |

| Table 7.1. Generated File List                                      |     |

| Table 8.1. PCIe LTSSM State and Sub-State Definition                | 273 |

| Table A.1. Lattice PCIe IP Core Resource Utilization                | 279 |

FPGA-IPUG-02243-1.3

# Acronyms in This Document

A list of acronyms used in this document.

| Acronym | Definition                                |

|---------|-------------------------------------------|

| ASPM    | Active State Power Management             |

| AXI     | Advanced Extensible Interface             |

| AXI-L   | Advanced Extensible Interface Lite        |

| BAR     | Base Address Register                     |

| CSR     | Configuration and Status Register         |

| DLLP    | Data Link Layer Packet                    |

| DMA     | Direct Memory Access                      |

| ECC     | Error Correction Coding                   |

| EP      | Endpoint                                  |

| FIFO    | First In First Out                        |

| LMMI    | Lattice Memory Mapped Interface           |

| LTSSM   | Link Training and Status State Machine    |

| MSI     | Message Signaled Interrupt                |

| RTL     | Register Transfer Language                |

| PCI     | Peripheral Component Interconnect         |

| PCIE    | Peripheral Component Interconnect Express |

| PCS     | Physical Coding Sublayer                  |

| PLL     | Phase-Locked Loop                         |

| PM      | Power Management                          |

| PMA     | Physical Medium Attachment                |

| RAM     | Random Access Memory                      |

| RC      | Root Complex                              |

| RP      | Root Port                                 |

| TLP     | Transaction Layer Packet                  |

# 1. Introduction

## 1.1. Overview of the IP

PCI Express<sup>®</sup> is a high performance, fully scalable, and well-defined standard for a wide variety of computing and communications platforms. As a packet-based serial technology, the PCI Express standard greatly reduces the number of required pins and simplifies board routing and manufacturing. PCI Express is a point-to-point technology, as opposed to the multi-drop bus in PCI. Each PCI Express device has the advantage of full duplex communication with its link partner to greatly increase overall system bandwidth. The basic data rate for a single lane is double that of the 32-bit/33 MHz PCI bus. A four-lane link has eight times the data rate in each direction of a conventional bus.

The Lattice PCIe x8 IP Core provides a flexible, high-performance, easy-to-use Transaction Layer Interface to the PCI Express Bus. The Lattice PCIe x8 IP Core implementation is a hardened IP with soft logic provided for interface conversion options. The hardened IP is an integration of PHY and Link Layer blocks.

The Lattice PCIe x8 IP Core is supported in the Lattice Avant<sup>™</sup>-AT-G and Lattice Avant-AT-X FPGA device family and is available in the Lattice Radiant<sup>™</sup> software.

## 1.2. Quick Facts

#### Table 1.1. Summary of the PCIe x8 IP

| IP Requirements      | Supported FPGA Families  | Avant-AT-G, Avant-AT-X                                      |  |  |

|----------------------|--------------------------|-------------------------------------------------------------|--|--|

|                      | IP Changes               | Refer to the PCIe x8 IP Release Notes (FPGA-RN-02061).      |  |  |

| Resource Utilization | Targeted Devices         | All Avant-AT-G and Avant-AT-X family                        |  |  |

|                      | Supported User Interface | LMMI, AXI-L, TLP, AXI4-Stream                               |  |  |

|                      | Lattice Implementation   | IP Core v2.2.0 – Lattice Radiant Software 2024.2.1 or later |  |  |

| Design Tool Support  | Synthesis                | Lattice Synthesis Engine                                    |  |  |

| Design Tool Support  | Synthesis                | Synopsys <sup>®</sup> Synplify Pro <sup>®</sup> for Lattice |  |  |

|                      | Simulation               | Questasim                                                   |  |  |

### **1.3.** IP Support Summary

| Device Family            | IP          | User<br>Interface | Gen Speed | Link Width     | Data Rate<br>(Gbps) | Radiant<br>Timing Model | Hardware<br>Validated |

|--------------------------|-------------|-------------------|-----------|----------------|---------------------|-------------------------|-----------------------|

| Avant-AT-G<br>Avant-AT-X | PCIe EP     | TLP               | Gen 4     | X8, X4, X2, X1 | 128, 64, 32,<br>16  | Preliminary             | No                    |

|                          |             |                   | Gen 3     | X8, X4, X2, X1 | 64, 32, 16, 8       | Preliminary             | No                    |

|                          |             |                   | Gen 2     | X8, X4, X2, X1 | 40, 20, 10, 5       | Preliminary             | No                    |

|                          |             |                   | Gen 1     | X8, X4, X2, X1 | 20, 10, 5, 2.5      | Preliminary             | No                    |

|                          |             | AXI-Stream        | Gen 4     | X8, X4, X2, X1 | 128, 64, 32,<br>16  | Preliminary             | No                    |

|                          |             |                   | Gen 3     | X8, X4, X2, X1 | 64, 32, 16, 8       | Preliminary             | No                    |

|                          |             |                   | Gen 2     | X8, X4, X2, X1 | 40, 20, 10, 5       | Preliminary             | No                    |

|                          |             |                   | Gen 1     | X8, X4, X2, X1 | 20, 10, 5, 2.5      | Preliminary             | No                    |

|                          | PCIe Harden | AXI-MM            | Gen 4     | X8             | 128                 | Preliminary             | No                    |

|                          | DMA         |                   | Gen 3     | X8             | 64                  | Preliminary             | No                    |

|                          |             |                   | Gen 2     | X8             | 40                  | Preliminary             | No                    |

|                          |             |                   | Gen 1     | X8             | 20                  | Preliminary             | No                    |

## 1.4. Features

The Hard IP PHY key features include:

- Aggregation and bifurcation up to x4 lanes and x8 lanes PHY configuration

- Data rates of 2.5 Gbps, 5.0 Gbps, 8.0 Gbps, and 16.0 Gbps

- Selectable parallel data widths such as 8, 16, 32, 64

- 8b/10b encoding at 2.5 Gbps and 5 Gbps, and 128b/130b encoding at 8 Gbps and 16 Gbps

- Adaptive and configurable RX Continuous Time Linear Equalizer (CTLE) and Decision Feedback Equalizer (DFE)

- Adaptive and programmable TX equalization

- PCIe L1-substate power managements and Separate RefClk Independent SSC Architecture (SRIS)

- Extensive PMA debug capability via read/write and read-only registers in PCS

- Register-based control of all PCS-to-PMA signals

- A wide range of reference clock frequencies with optional fractional frequency correction capability

- A wide range of divided clock frequencies for external-to-PHY usage with optional spread-spectrum clock (SSC) capability

- Built-in, on-chip SSC generation and full configuration from –5000 to +5000 ppm

- Test support features such as near-end loopback, PLL bypass modes, and others.

- Protocol-compatible features such as LOS, squelch, power modes, and others.

The Hard IP Link Layer key features include:

- PCI Express Base Specification Revision 4.0 compliant including compliance with earlier PCI Express Specifications.

- Backward compatible with PCI Express 3.x, 2.x, 1.x

- x8 PCI Express Lanes with support for bifurcation

- Supported lane configurations:

- Radiant 2023.2 1 × 4, 1 × 2, 1 × 1

- Radiant 2024.1 and future Radiant releases 1 × 8, 1 × 4, 1 × 2, 1 × 1

- 16.0GT/s, 8.0GT/s, 5.0 GT/s, and 2.5 GT/s line rate support

- Comprehensive application support:

- Endpoint

- Root Port (future release)

- Multi-Function support per link

- PCIe x8 Core supports 1-8 PF

- PCIe x4 Core supports 1-8 PF

- SRIOV support per link (future release for non-DMA)

- PCIe x8 Core supports up to 32 (PF+VF) functions

- PCIe x4 Core supports up to 32 (PF+VF) functions

- Support for Autonomous and Software-Controlled Equalization

- Support for Figure of Merit and Up/Down PIPE PHY Equalization

- Flexible Equalization methods (Algorithm, Preset, User-Table, Adaptive-Table, Firmware-controlled)

- ECC RAM and Parity Data Path Protection

- Core Data Width

- 64 bits for x1 lane

- 128 bits for x2 lanes

- 256 bits for x4 lanes

- 512 bits for x8 lanes

- Complete error-handling support

- AER, ECRC generation/checking, recovery from Parity and ECC errors

- Supports detection of numerous optional errors, embedded simulation error checks/assertions

- Simulation and hardware error injection features enable error testing

- Flexible core options allow for design complexity/feature tradeoffs

- Configurable Receive, Transmit, and Replay Buffer sizes

- Supports Polarity Inversion, Up/Down-configure, Autonomous Link Width/Speed changes

- Power Management

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

- Supports L1, ASPM L0s, and ASPM L1

- L1 PM Substates with CLKREQ

- Power Budgeting

- Dynamic Power Allocation

- Latency Tolerance Reporting

- Implements Type 0 Configuration Registers in Endpoint Mode

- Implements Type 1 Configuration Registers in Root Port Mode (future release)

- Complete Root Port Configuration Register implementation (future release)

- Dual mode design supports EP or RP through register changes (future release)

- Easy to use

- Decodes received packets to provide key routing (BAR hits, Tag, and others) information

- Implements all aspects of the required PCIe Configuration Space

- Optionally consumes PCI Express Message TLPs or leaves them in band

- Interfaces have consistent timing and function over all modes of operation

- Provides a wealth of diagnostic information for superior system-level debug and link monitoring

- Implements all three PCI Express Layers (Transaction, Data Link, and Physical)

- Hardened high-performance multi-channel scatter-gather DMA controller

- Support up to 64 DMA channels

- Support for PCIe multi-function and SR-IOV capability

- 64-bit address support

#### 1.4.1. Hard IP Limitations

The following are the limitations of the Hard IP:

- Users can only access Function 0 of the PCIE Configuration Space Registers due to address bit limitation in Hard IP. This

affects the usage of links other than Link 0 since it relies on register interface to get a particular function setting (for

example, Max payload size and MSI/MSI-X configuration) including error reporting (AER).

- CLKREQ is not supported in MPPHY, reference clock stopping during L1 substate is not supported.

- AXI Write and Read address channel are sharing the same ports. Request will be done one at a time or sequentially cannot be simultaneous.

- DPA and LTR interface of the Hard IP are not exposed/available to the user.

- The Link Layer port \*p\_ clk\_period\_in\_ps is not programmable (hard coded). This may have an effect in timeout calculations.

- Reset ports are currently not exposed/available to the user.

- DMA is supported only in x8 mode.

#### 1.4.2. Soft IP

- TLP Data Interface

- AXI4-Stream Data Interface Option

- LMMI Register Interfaces

- AXI-L Register Interface

Radiant 2024.1 SP1 requires a patch to work with PCIe\_x8 IP.

## 1.5. Licensing and Ordering Information

An IP specific license string is required to enable full use of the PCIe x8 IP in a complete, top-level design.

The IP can be fully evaluated through functional simulation and implementation (synthesis, map, place and route) without an IP license string. This IP supports Lattice's Hardware Support capabilities. You can create versions of the IP to operate in hardware for a limited time (approximately four hours) without requiring an IP license string. A license string is required to enable timing simulation and to generate a bitstream file that does not include the hardware evaluation timeout limitation.

For more information about pricing and availability of the PCIe x8 IP, contact your local Lattice Sales Office.

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

### 1.5.1. Ordering Part Number

#### Table 1.2. Ordering Part Number

| Device Family | Part Number          |                    |

|---------------|----------------------|--------------------|

|               | Multi-Site Perpetual | Single Seat Annual |

| Avant-AT-G    | PCI-EXP8-AVG-UT      | PCI-EXP8-AVG-US    |

|               | PCI-EXP4-AVG-UT      | PCI-EXP4-AVG-US    |

|               | PCI-EXP2-AVG-UT      | PCI-EXP2-AVG-US    |

| Avant-AT-X    | PCI-EXP8-AVX-UT      | PCI-EXP8-AVX-US    |

|               | PCI-EXP4-AVX-UT      | PCI-EXP4-AVG-US    |

|               | PCI-EXP2-AVX-UT      | PCI-EXP2-AVG-US    |

## **1.6.** Hardware Support

Refer to the Example Design section for more information on the boards used.

## 1.7. Speed Grade Supported

The Lattice PCIe IP core supported speed grade is provided in this section. Different configurations may be supported using different speed grade due to fabric performance requirement.

• 3 – fastest speed grade

#### Table 1.3. Lattice PCIe IP Core Supported Speed Grade

| PCle Core Config | Device Family | Speed Grade |

|------------------|---------------|-------------|

| Gen3x8           | Avant-AT-G    | 1/2/3       |

| Gen4x8           | Avant-AT-X    | 1/2/3       |

## 1.8. Naming Conventions

#### 1.8.1. Nomenclature

The nomenclature used in this document is based on Verilog HDL.

#### 1.8.2. Signal Names

- \_n are active low (asserted when value is logic 0)

- \_i are input signals

- \_o are output signals

# 2. Functional Description

## 2.1. PCIe IP Architecture Overview

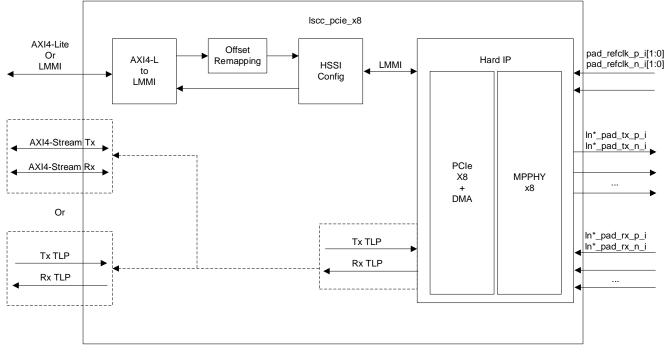

Figure 2.1. Lattice PCIe x8 IP Core Block Diagram

The Lattice PCIe x8 Core implements all three layers defined by the PCI Express specification: Physical, Data Link, and Transaction. Bifurcation is supported with link and lane configuration such as  $1 \times 8$ ,  $1 \times 4$ ,  $1 \times 2$ , and  $1 \times 1$ .

The Lattice PCIe x8 Core Hard IP implementation integrates the Rambus Expresso Core (Link Layer) and DMA controller, and Synopsys PMA and PCS Core (PHY). A block diagram with an 8-lane instance is shown in Figure 2.2.

For convenience, the Link Layer Cores are referred to as Link 0 – PCIe x8 Core.

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-IPUG-02243-1.3

| Multi-Protocol, Multi-Channel SerDes/PCS (MPPHY x8) |        |        |        |        |    |        |             |          |         |                  |

|-----------------------------------------------------|--------|--------|--------|--------|----|--------|-------------|----------|---------|------------------|

| QUAD 0                                              |        |        |        |        | [] | QUA    | D 1 (future | release) | <b></b> |                  |

| Common<br>Refclk                                    | LANE 0 | LANE 1 | LANE 2 | LANE 3 |    | LANE 4 | LANE 5      | LANE 6   | LANE 7  | Common<br>Refclk |

| PLL A                                               | PMA    | PMA    | PMA    | PMA    |    | PMA    | PMA         | PMA      | PMA     | PLL A            |

| PLL B                                               | PCS    | PCS    | PCS    | PCS    |    | PCS    | PCS         | PCS      | PCS     | PLL B            |

| Multi-Lane PCIe Core (PCIe x8 + DMA)      |  |

|-------------------------------------------|--|

| PCIe Core<br>x8                           |  |

| DMA Core (Bypassable)<br>(future release) |  |

|                                           |  |

| FPGA Fabric                               |  |

#### Figure 2.2. Lattice 8-lane SERDES/PCS + PCIe Hard-IP

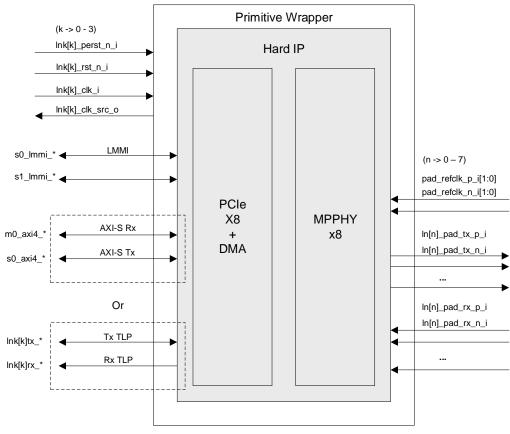

The Lattice PCIe x8 Core Hard IP has the following interfaces as shown in Figure 2.3. The details of each interface are discussed in the following sections.

Figure 2.3. Lattice PCIe x8 Core Hard IP

- Clock and Reset Interface

- The user domain interface can be clocked using one of several PHY clock outputs (syc\_clk\_i = link0\_clk\_src\_o) or by user-generated clock. The fundamental reset (link0\_perst\_n\_i) resets the core (PHY and Link layer blocks) except for the core Configuration Registers. Another reset (link0\_rst\_usr\_n\_i) is provided to reset only the Link layer block.

- PHY Interface

- High Speed Serial Interface supports maximum rate of 16GT/s

- Up to eight lanes (grouped into Two Quads)

- TLP Receive Interface

- Receive TLPs from the PCIe link partner

- High bandwidth interface

- 512b data width (64b per active lane)

- TLP Transmit Interface

- Transmit TLPs to the PCIe link partner

- High bandwidth interface

- 512b data width (64b per active lane)

- Power Management Interface Not Supported

- Ports for implementing power management capabilities

- AXI Interface

- Available if Hard DMA Core is enabled

- 512b data width each (TX and RX)

- AXI4-Lite or LMMI (Mutually exclusive) Configuration and Status Register (CSR) Interface

- This interface is used to write and read the core configuration and status registers. A typical customer application requires changing only a small number of the default values such as Vendor ID, Device ID, and BAR configuration.

- 32b data width (AXI4-Lite) or 16b data width (LMMI)

## 2.2. Clocking

#### 2.2.1. Clocking Overview

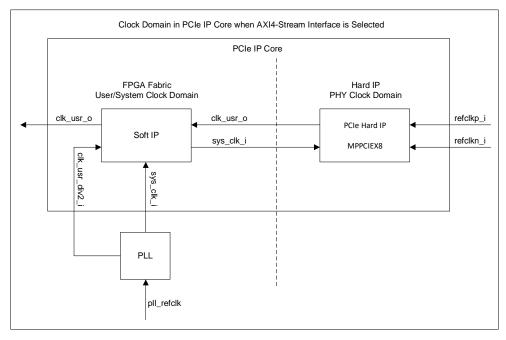

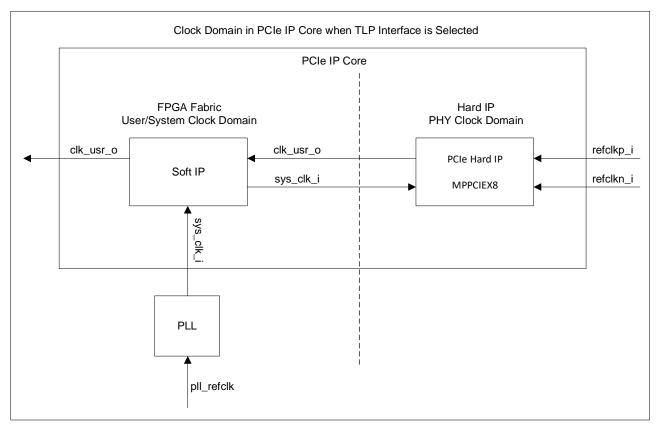

Figure 2.5. PCIe IP Clock Domain Block Diagram for TLP Interface

The PCIe x8 IP includes the following clock domains. The *sys\_clk\_i* and *clk\_usr\_div2\_i* signals are generated during the PLL IP instantiation. For the TLP interface, you can connect *clk\_usr\_o* back to the *sys\_clk\_i*, as shown in Figure 2.5.

- refclkp\_i/refclkn\_i are differential PHY reference clocks.

- You can set the reference clock frequency in the PCIe IP Core.

- There are two options available: 100 MHz or 125 MHz.

- sys\_clk\_i/clk\_usr\_i is the user clock domain input clock.

- This clock is generated by the system PLL and shared to the Link layer blocks.

- For the TLP interface variants, you can choose to connect *clk\_usr\_o* back to the *sys\_clk\_i* as shown in Figure 2.5.

- clk\_usr\_div2\_i is the user clock domain divided by two input clocks.

- This clock is generated by the system PLL with simple division by two at half of the sys\_clk\_i frequency.

- This clock does not apply to the TLP interface variants.

- •

- clk\_usr\_o\_is the User Clock Domain Output Clock.

- This is the pclk output that comes from the PHY of the PCIe IP core.

- By default, *clk\_usr\_o* uses the divide-by-2 version of the 125 MHz pclk from the PHY.

## 2.3. Reset

#### 2.3.1. Reset Overview

There are two fundamental reset events that can occur in PCI Express:

- Cold Reset This is a fundamental reset applied during power cycling. The signal link [LINK]\_perst\_n\_i is asserted.

- Warm Reset This is a fundamental reset triggered by hardware without the removal and re-application of power. The

perst\_n\_i signal is asserted.

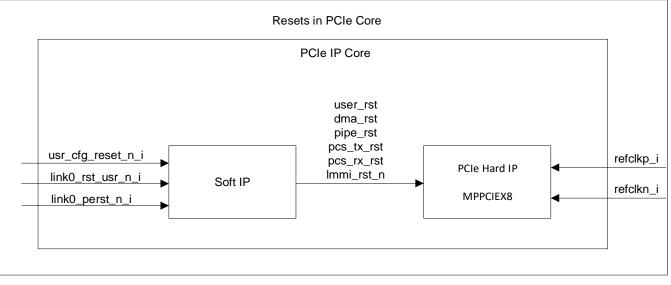

The fundamental reset *link* [*LINK*]\_*perst\_n\_i* resets the core (Link Layer and PHY Layer blocks) while another reset, which is the user clock domain Link Layer reset [*LINK*]\_*rst\_usr\_n\_i*, is used to reset the Link Layer block only.

Depending on the PCIe IP configuration, either DMA or non-DMA, reset signal *usr\_cfg\_reset\_n\_i* is used.

Figure 2.6. Reset Signals in Lattice PCIe IP Core

© 2025 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-IPUG-02243-1.3

LATTICE

### 2.3.2. Clock and Reset Sequence

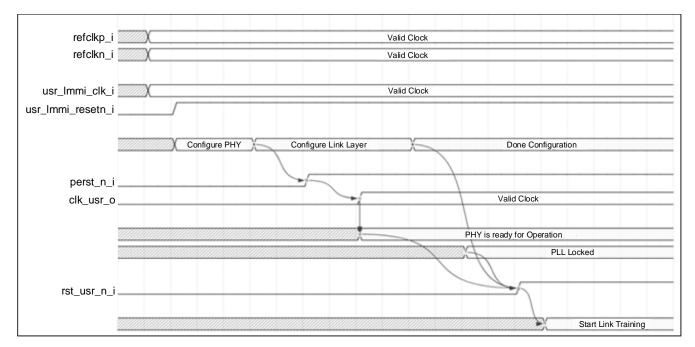

The PCIe IP clock and reset operation is shown in Figure 2-7.

Figure 2-7. Clock and Reset Sequence Diagram

The Lattice PCIe x8 IP Core configuration register implementation has default values that are appropriate for most applications. You can change the register configuration through the LMMI or AXI-L interface. When the LMMI or AXI-L interface is used to configure the PHY layer registers, the configuration should be done before the deassertion of the *link0\_perst\_n\_i* signal. The PHY Layer is released from reset and is ready for operation once it is able to generate the PIPE clock output (such as the link0\_clk\_usr\_o signal). The user domain reset (such as *link0\_rst\_usr\_n\_i*) can be deasserted if the Link Layer register configuration is done or skipped.

To ensure that the clock is stable before the link training, you must wait for the PLL locked status for all four channels of Tx PLL before de-asserting the user domain reset (*link0\_rst\_usr\_n\_i*). If you select the x2 or x1 link width, you may observe the two-channel Tx PLL locked status or one channel Tx PLL locked status respectively. The TX PLL status (*bit-4, offset 0x7F in PHY PMA Status register*) can be read through the LMMI or AXI-L.

## 2.4. Protocol Layers

There are three major classes of packets in PCIe devices: Transaction Layer Packets (TLP), Data Link Layer Packets (DLLP, and Physical Layer Packets (PLP), which is also known as ordered sets). The function of the Protocol Layer is to generate and process these packets.

• Transaction Layer

The Transaction Layer manages the TLPs to communicate request and completion data with other PCIe devices. The TLP packets are assembled at the *transmit side* of the link and disassembled at the *receive side* of the link. The TLP communicates through different formats either in I/O request format or in the memory request format.

• Data Link Layer